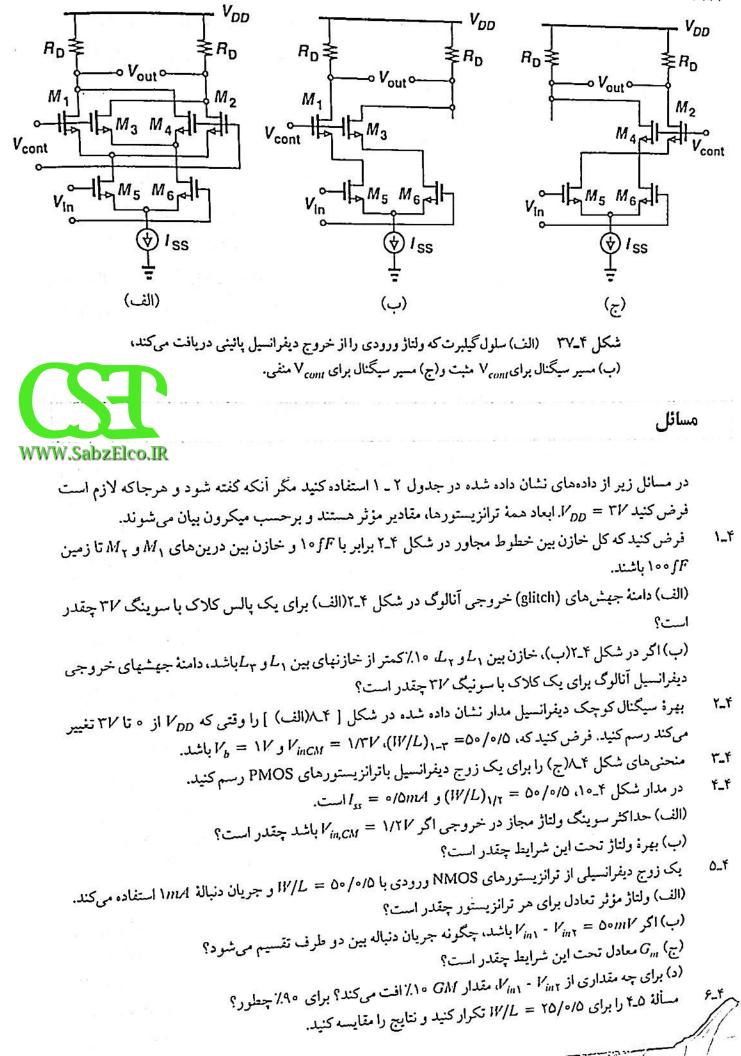

\_\_\_\_

۷.۲ مسأله ۵-۴ را با جریان دنبالهٔ ۲۳۸۱ تکرار کنید و نتایج را مقایسه کنید.

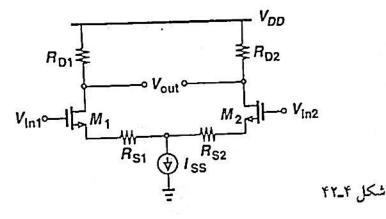

$R_{ss}$  مدار شکل ۲۸.۴ را با فرض اینکه ۵/۰/ ۵۰ – ۵۵ – ۱/۲ (W/L) و ۲KΩ ج نمایانگر امپدانس خروجی یک منبع جریان NMOS با ۵/۰/ ۵۰ =  $R_{ss}$ باشد در نظر بگیرید. فرض کنید که  $R_{ss}$  نمایانگر امپدانس خروجی یک منبع جریان NMOS با ۵/۰/۵۰ و ۵/۳ (W/L) و جریان درین ۱۳۸۸ باشد. سیگنال ورودی شامل  $V_{II}$  (III/L) است که  $V_{II}(I)$  و جریان درین ۱۳۸۸ باشد. سیگنال اور در شامل  $V_{II}(I)$  است دامنه نویز با سر به سر  $V_{III,CM} = 1/0$  ( $V_{II}(I)$  است که  $V_{II}(I)$  ( $V_{III}(I)$  ( $V_{II}(I)$ ) و جریان درین ۱۳۸۸ باشد. سیگنال ارودی شامل  $V_{II}(I)$  ( $V_{III}(I)$ ) و  $V_{III,CM} = 10$  ( $V_{III}(I)$ ) و جریان درین ۱۰۵ باشد. سیگنال  $V_{III}(I)$  ( $V_{III}(I)$ ) و جریان درین ۱۰۵ باشد. سیگنال  $V_{III}(I)$  ( $V_{III}(I)$ ) و جریان دامنه نویز با سر به سر  $V_{III}(I)$  ( $V_{III}(I)$ ) ( $V_{III}(I)$ ) و جریان دامنه نویز با سر به سر  $V_{III}(I)$  ( $V_{III}(I)$ ) ( $V_{IIII}(I)$ ) ( $V_{III}(I)$ ) ( $V_{IIII}(I)$ ) ( $V_{III}(I)$ ) (V

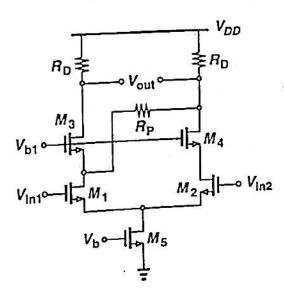

۱۱.۴ فرض کنید که زوج دیفرانسیل شکل ۳۲-۱(الف) با ۰۵/۵/۵۵=۱/۲(*W/L*)، ۵/۰/۵۰=۱/۳(*W/L*) و ۱۱.۴ طراحی شده است. همچنین *Iss ب*ایک ترانزیستور NMOS که ۰۵/۵/۵۵=۱*۷(W/L)* است، ساخته شده است. (الف) اگر سوینگهای دیفرانسیل در ورودی و خروجی کوچک باشند، کمترین و بیشترین سطوح CM مجاز در ورودی کدامند.

- ۱۲\_۴ در مسالهٔ ۲\_۱۱، فرض کنید که عدم تطابق بین ولتاژ آستانهٔ M<sub>۱</sub> و M<sub>۲</sub> برابر با ۱*m۷* باشد. CMRR چقدر است؟

- ۱۳-۴ در مسألهٔ ۱۱\_۴، فرض کنید که ۷۴ = ۱۰۴ ولی ۱۱۴ = ۱۴ باشد. CMRR را حساب کنید؟

$$\left(\frac{W}{L}\right)_{\tau/\tau} = \frac{\Delta \cdot}{\sqrt{2}} \int \left(\frac{W}{L}\right)_{1/\tau} = \frac{\Delta \cdot}{\frac{1}{\sqrt{2}}}$$

باشد حساب کنید. اگر <sub>ss</sub> ابه حداقل /۴۱/ه روی آن نیاز داشته باشد، حداقل سطح CM مجاز در ورودی چیست؟ با استفاده از مقدار V<sub>in,CM</sub>، سونیگ خروجی حداکثر را درهر حالت حساب کنید؟

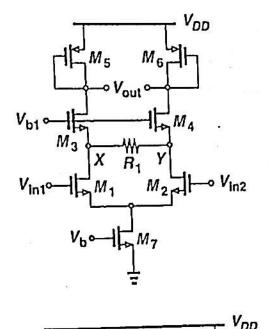

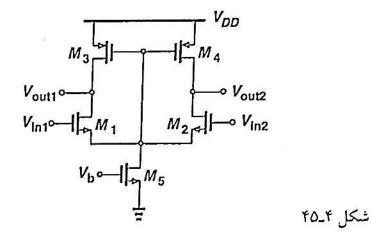

I<sub>ss</sub> = ۱mA در مدار شکل ۲۳۳۴، فرض کنید که برای همهٔ ترانزیستورها، ۵/۰/۵ = ۵/۱۷ است و ۱mA = ss (الف) بپرهٔ ولتاژ را حساب کنید. (ب) V<sub>b</sub> را طوری حساب کنید که:

$$I_{D\Delta} = I_{DF} = \cdot / \Lambda \left( I_{ss} / \Upsilon \right)$$

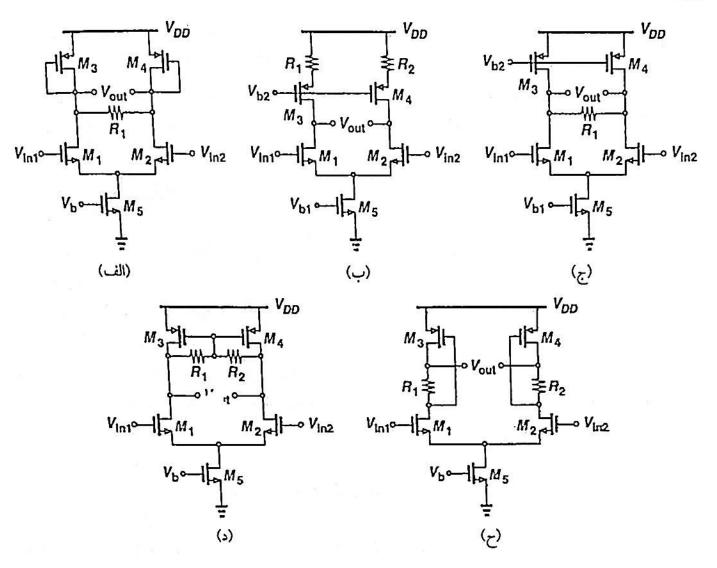

(ج) اگر <sub>sr</sub> به حداقل ولتاژ ۷۴/۰ نیاز داشته باشد، حداکثر سوینگ دیفرانسیل در خروجی چیست؟ V<sub>in1</sub> با فرض اینکه همهٔ مدارهای نشان داده شده در شکل ۳۸٫۴ متقارن هستند، سر را برحسب (الف) ۷<sub>in1</sub> و ۱۶٫۴ وقتی که بطور دیفرانسیلی از ۲۰ تا V<sub>DD</sub> تغییر میکنند و (ب) ۷<sub>in1</sub> و ۷<sub>in۲</sub> وقتی که برابر باشند و از ۲۰ تا V<sub>DD</sub> تغییر کنند، رسم کنید.

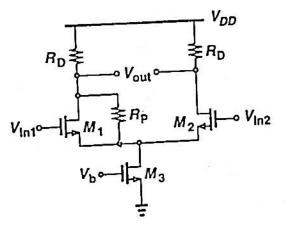

۲۹-۴ با فرض اینکه همهٔ مدارهای نشان داده شده در شکل ۲۹-۴ متقارن باشند، ۷<sub>00</sub>۷ را برحسب (الف) ۷<sub>in</sub>۱ و ۱۷-۴ وقتی که بطور دیفرانسیلی از ۵ تا ۷<sub>DD</sub> تغییر میکنند، رسم کنید (ب) ۷<sub>in</sub>۱ و ۷<sub>in</sub>۲ وقتی که برابر باشند و از ۵ تا ۷<sub>DD</sub> تغییر کنند، رسم کنید.

شکل ۲۸۴

- ۱۸۰۴ فرض کنید که همهٔ ترانزیستورهای شکل ۲۹۸۴ و ۲۹۳۴ در اشباع باشند و ۵ ≠ ۶ بهرهٔ ولتاژ دیفرانسیل سیگنال کوچک هر مدار را حساب کنید.

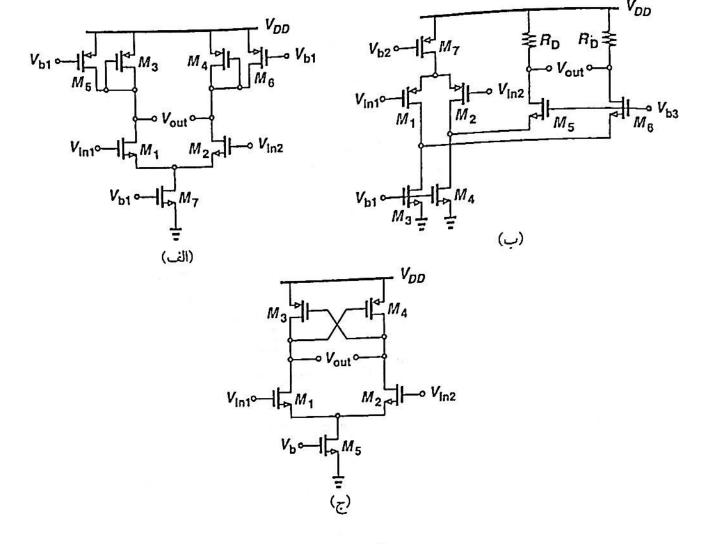

- ۱۹\_۴ مدار شکل ۴\_۴۰ را در نظر بگیرید. (الف) <sub>000</sub> را برحسب <sub>۱۱۱</sub> و ۷<sub>۱۱۲</sub> و قتی که بطور دیفرانسیلی از ۵ تا <sub>DD</sub> تغییر میکنند، رسم کنید. (ب) اگر ∞ = ۶۰ یک رابطه برای بهره ولتاژ بدست آورید. اگر ۱۸<sub>۶% ۱</sub>۸۱۴ = ۲<sub>۳۱۴</sub> باشد، بهرهٔ ولتاژ چقدر است؟

- ۲۰-۴ برای مدار شکل ۲۱\_۴ (الف)<sub>00</sub>۷ و ۷<sub>۲</sub>۷ و ۷۷ را برحسب ۷<sub>in۱</sub> و ۷<sub>in۲</sub> وقتی که بطور دیغرانسیلی از ۰ تا ۷<sub>DD</sub> تغییر کنند، بدست آورید. (ب) بهرهٔ ولتاژ سیگنال کوچک دیفرانسیل را بدست آورید.

- ۲۱\_۴ با فرض اینکه مدار شکل ۲۴\_۲۴ متقارن نیست و بدون استفاده از مدار معادل، بهرهٔ ولتاژ سیگنال کوچک (۷<sub>in۲</sub> -۲۱\_۴ (۱<sub>om</sub>)/(۷<sub>in۱</sub>) را اگر ۰ = ۶ و ۰ ≠ ۲ باشد، بدست آورید.

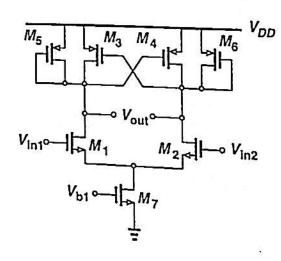

- ۲۲-۴ به دلیل خطاهای ساخت، یک مقاومت پارازیتی بین ترمینالهای درین و سورس M<sub>۸</sub> در شکل ۴۳-۴ بوجود آمد. است. با فرض اینکه ۰ = ۲ = ۶ بهرهٔ سیگنال کوچک، بهرهٔ مُد مشترک و CMRR را حساب کنید.

- ۲۳-۴ به دلیل خطاهای ساخت، یک مقاومت پارازینی بزرگ درین های M<sub>۱</sub> و M<sub>۲</sub> در مدار شکل ۴۴-۴۴ پدیده آمده است. با فرض اینکه ۰ = ۷ = ۸ بهرهٔ سیگنال کوچک، مد مشترک و CMRR را حساب کنید.

- ۲۴-۴ در مدار شکل ۲۵-۴، (۱۷/L) هنمهٔ ترانزیستورها ۵/۰/۵۵است و M<sub>e</sub>و M<sub>e</sub>باید در ناحیهٔ تریود عمیق و با مقاومت روشن ۲KΩ کار کنند. با فرض ۰ = γ = ۶ سطح مُد مشترک ورودی را که چنین مقاومتی را ایـجاد میکند،

شکل ۲۹\_۴

شکل ۴-۴

شکل ۲۱\_۴

شکل ۴۳\_۴

شکل ۴۴\_۴

1411

مراجع

P.R.Gray and R.G.Meyer, Analysis and Design of Analog Integrated Circuits, Third Ed., NeW York: Wiley, 1993

B.Gilbert, "A Precise Four - Quadrant Multiplier With Subnanosecond Response," IEEE J.Solid -State Circuits, VoL.SC - 3, PP.365-373, Dec.1968